David Brunco, Ph.D

Principal IP Technologist

Cornell University, Ithaca, NY

● Ph.D, Materials Science and Engineering

Massachusetts Institute of Technology, Cambridge, MA

● BS, Materials Science and Engineering

David has over 25 years of semiconductor device pathfinding and exploratory research, product development, and manufacturing as a principal technologist. He has collaborated with technologists on advanced semiconductor research projects at Intel, GlobalFoundries, IMEC, and IBM Alliance. David has developed FinFET devices, integration processes, and manufacturing equipment designs for memory (Flash) and processor (CPU and GPU) products. He has 30 patents and over 75 technical publications related to semiconductor structures and fabrication.

David leverages his semiconductor research and development background to provide patent engineering for invention mining and prior art searches, and to support patent attorneys on patent drafting, licensing, pre-litigation, and litigation matters in the semiconductor industry. His extensive semiconductor background enables him to strategically craft broad, patentable claims with detectable features for developing higher value, enforceable semiconductor patents.

Representative Semiconductor & Patent Experience

Device Structures, Process Integration, and Equipment Design

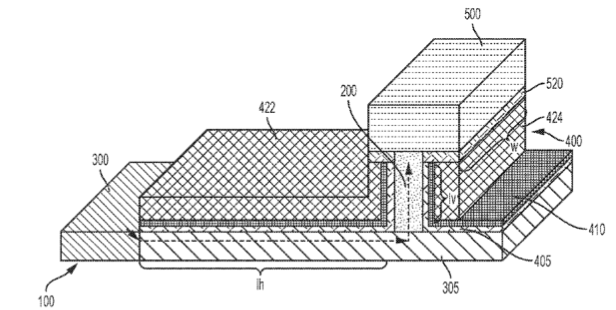

- Semiconductor pathfinding and exploratory research for advanced planar and fin field-effect transistor (FinFET) technology (including device structures, process integration and equipment designs) to meet cost, performance, and functionality requirements for new product applications. Initiated front end exploratory research team for pathfinding.

- Collaborated with front end of line (FEOL) pathfinding research teams to explore SiGe, Ge, and III-V materials, strain engineering, and dopant profile optimization (super steep retrograde well – SSRW) for high mobility channel devices. Researched and developed back end of line (BEOL) metal-insulator-metal (MIM) capacitor stacks using multiple atomic layer deposition (ALD) dielectrics to achieve product specifications. Inventor of patented high-mobility channel architecture and SSRW framework used by the IBM Research Alliance.

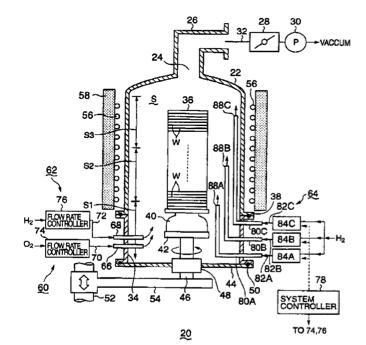

- Logic and flash memory researcher – chaired High-Quality / High-k research team at an international research & development consortium (IMEC in Belgium). Improved HfO2 quality with optimization of atomic layer deposition (ALD) growth conditions and reduced equivalent oxide thickness (EOT) growth through degas Drove improvements to IMEC’s Germanium program which resulted in world-leading process and performance. Investigated high k dielectrics for floating gate and nitride flash memories, enabling down selection of strategies for future flash memory technologies.

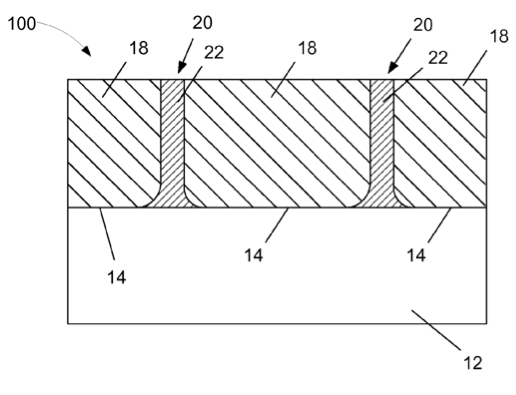

- Led development team with contributors from integration, process engineering, device, and technology computer aided design (TCAD) functions to develop shallow trench isolation (STI), Well, and Fin Reveal modules for 7 nm node FinFETs. Chaired development change review board (DCRB) for 7 nm FEOL.

- Led radical oxidation tool selection team and subsequent process implementation to improve shallow trench isolation (STI) liner and tunnel oxide modules for 90 nm (and beyond) Flash products. Owned rapid thermal process (RTP) on multiple logic and flash technologies, driving improvements to product performance, yield, process control, run rate, manufacturability and cost.

- Post-doctoral research at Varian Semiconductor. Characterized, improved uniformity, and reduced contamination for plasma doping (PLAD). Converted alpha tool from 150 to 200-mm wafer processing.

- Doctoral research covering nonequilibrium solidification of nondilute alloys: measurements in SiGe alloys and extensions of interface stability theories. Research projects included device fabrication, laser processing, and theory collaboration between Cornell and Harvard researchers.

Patent Engineering & Analytics

- Served as technical chair for FinFET patent review committee at GlobalFoundries. Improved decision quality through higher standards for committee membership and more rigorous pre-review methodology.

- Analyzed semiconductor patent portfolios to identify higher value patents for supporting licensing or acquisition diligence based on claim quality, product usage, and business impact.

- Analyzed reverse engineering (RE) data from unlicensed products against patent portfolios of interest to support patent licensing programs. Identified RE data gaps and opportunities to strengthen patent claim charts against unlicensed products.